近来全球重新认知半导体的战略重要性,其中台湾的存在感更不容忽视,最具代表性的就是全球顶级半导体代工厂如联华电子(UMC)、台积电(TSMC),然而在幕后提供相关支援,使台湾相关企业能在半导体领域持续领跑的工业技术研究院(ITRI,以下简称ITRI)也功不可没。ITRI已有50多年的历史,是众多新创企业的摇篮,并大力协助相关产业化过程。本次专访ITRI电子与光电系统研究所张世杰所长,畅谈一直以来ITRI在号称全球最先进的台湾半导体产业领域扮演的角色,以及面对日新月异的半导体技术研究,包括最新趋势的异质整合(heterogeneous integration)在内,ITRI又如何看待本身定位。

(受访者简历)

工业技术研究院 电子与光电系统研究所所长

张世杰(Shih-Chieh Chang)

2022年就任ITRI电子与光电系统研究所所长,致力投入半导体、AI等新兴技术开发,率领团队描绘技术蓝图,启动AI芯片关键技术研发,确立国家层级技术发展,促进实证计画的成功模式,对台湾半导体产业之自主研发影响匪浅。目前担任台湾人工智能芯片联盟(AI on Chip Taiwan Alliance,AITA)副会长兼执行秘书。

| 台湾半导体产业与ITRI

一般认为,之所以ITRI是台湾半导体产业的幕后推手,基于下列4大理由。首先, ITRI设有促进官民合作的相关部门。例如ITRI与产业合作,成功推动磁阻式随机存取记忆体(MRAM)※1的相关研究,研发出的MRAM不仅速度之快傲视全球,效率也高。其次,ITRI并获得国外资金援助,与国外大学合作进行MRAM相关研究,成功降低功耗。

其次,ITRI也获得政府资金挹注,同步推动先进半导体封装技术相关研究,并在此过程中积累了丰厚的技术、智财资产。ITRI不论在软硬体领域均拥有众多知识产权,通过把相关knowhow回馈业界,致力提升台湾半导体行业的整体技术水平。

第三个理由为培育相关人才,也许过去很少有人提及这一点,但我个人认为相当重要。一直以来,通过在ITRI参与主要技术研究的工程师独立创业,带动技术回馈,刺激产业整体进一步活跃发展。相关行业经营者不少都是ITRI出身,相关专利总数超过30,000件,每年技术移转件数也超过650件,独立企业总计240家, ITRI OB研究人员更超过6,000人。

最后,则不得不提到众多产学合作联盟的存在。相关联盟提供相关场域,让产业界、学术界及研发机构三者得以积极合作,进行技术交流。除了横向的技术交流外,还能促进纵向交流,例如系统厂商、零件厂商间合作。包括IC设计、Micro LED、显示器相关的多个联盟及化合物半导体联盟在内,目前ITRI参与的联盟至少超过10个,推动产学合作不遗余力。其中当然也包括近来备受瞩目的异质整合、芯粒(Chiplet)封装等相关联盟,以及车载相关联盟。作为台湾代表性研究机构,ITRI主动通过参与联盟促进相关生态体系构建,有助于加快半导体研发速度,并从中发掘众多潜藏的技术种子,带动技术进化。

| 备受瞩目的半导体先进封装开发课题与成果

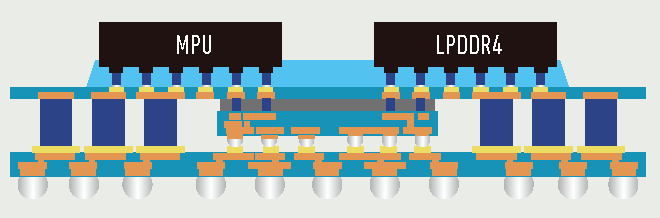

近年来,先进封装技术日新月异, 2.5D、3D、扇出型(Fan-Out)封装等技术各位应该也是耳熟能详。由于相关设计、流程复杂程度不可同日而语,以下想简单介绍封装工程师面对的相关课题,以及致力解决课题的相关研究成果。

首先,运用崭新设计方法时必须符合高密度化、精密度提升要求,压缩技术※2及成本课题也应运而生,包括TSV※3制造成本昂贵,以及初期不见得能确保高良率。其次还面对散热课题,针对芯片集成封装,如何散热为重要课题。以下简单介绍ITRI面对课题,如何推动相关研究并取得成果。

先进半导体封装主要应用于多样少量产品制造,相关市场要求的技术水准逐年提升,顺应难度极高。

ITRI本身设有少量生产用2.5D、3D封装试产产线,不少业界人士对试产产线十分感兴趣,ITRI希望通过领先试产,致力支援业界推动产品量产化。

第二个成果则是芯粒相关开发。为了降低功耗以及追求性能提升,半导体代工行业持续推动制程改良,但成本却也随之节节攀升。尤其是半导体行业奉为圭臬的摩尔定律越接近3纳米越面临极限,制程微缩已不再是问题解决的万灵丹,众多业界人士期待芯粒有助于突破摩尔定律极限。

第三个成果的相关技术已经在市场上流通,前面也曾提到矽中介层庞大且昂贵;相较之下,同样作为2.5D封装技术,因特尔的嵌入式多芯片互联桥接(Embedded Multi-die Interconnect Bridge,EMIB)技术不使用矽中介层,而是在封装树脂基板埋设名为「硅桥(silicon bridge)」的小型硅基板,得以降低制造成本。虽然仅限无需高速通信的产品使用,但因为使用低速互连而能降低价格,带动EMIB普及。很巧的是ITRI也提出与英特尔EMIB概念接近的EIC(Embedded Interposer Carrier) 架构,但ITRI比英特尔更早取得专利(快2~3周)。与EMIB的不同处则在于EIC利用重新布线(Redistribution layer,RDL)※4,布线能直达下方硅桥(EIC),无须重新设计芯片本身。

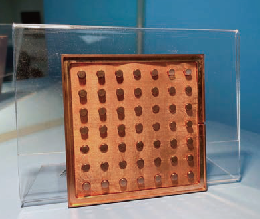

顺应散热课题的研究成果方面,向各位介绍名为 TGP的薄型均温板(金属盖)。芯粒采用集成结构,难以散热,因此思考如何散热为重要课题。为了解决此课题,ITRI开发了能贴在芯片上的TGP。TGP也采取多层结构,中间利用毛细管现象※5散热。TGP中含水,芯片发热导致水蒸发,向上移动散热。水蒸气冷却后又变回水,循环使用。ITRI与台湾规模最大的散热设备企业合作,目标为量产TGP。现阶段TGP已经能进行超过200W的散热,今后预计进一步改良,将对应散热量提升到400W以上。以上是针对ITRI在半导体领域的先进技术研究成果简单介绍。

|

|

|

| 具专利架构的TGP Lid元件 | TGP Lid实际用于芯片上 |

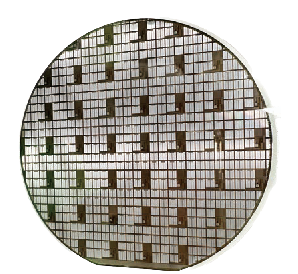

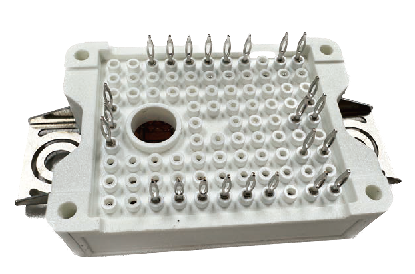

| 伴随EV普及乍然成为瞩目焦点的功率半导体

近年来伴随EV普及,功率半导体成为瞩目焦点,尤其功率模组封装更是对应电动车需求的关键。

个人认为日本、欧洲在相关领域的技术十分先进,台湾也以黑马之姿迎头赶上。

功率元件及模组化重视散热及可靠性问题,特别是功率元件高度发热,必须采取相关对策,以免因过热影响整体安全及性能。

ITRI在功率模组封装多年投入相当多的关键制程研究,包括芯片接合确保电性导通,材料与封装结构匹配度的最佳化处理,以掌握良好的散热效果及稳定性。

关于芯片接合工程方面, ITRI曾与日本三井金属共同研究铜烧结制程与材料,实证可将碳化硅芯片接合的孔隙率降到低于3%以下,此成果也持续导入于ITRI受托的功率模组试制品项目。

同时,积累的经验已获得不少车载关键零部件厂商青睐,委托终端应用开发方案不在少数。

比如自主开发的高压碳化硅元件并进行模组化工程后,整合到EV车用充电桩的实际案例,预定在今年(2023年)10月于名古屋电动车大展会中公开。

|

|

|

| 工研院设计开发的碳化硅晶圆 | EV车用充电桩的碳化硅功率模组 |

| 对电子设计自动化(EDA)进化而言,供应商与设计人员的合作不可或缺

以上介绍的是过去ITRI的半导体行业相关对策及成果,最后想跟各位聊聊对相关研究而言不可或缺的电子设计自动化(EDA)。不论对半导体制造上游的IC设计公司或下游的代工厂商而言,EDA都是非常重要的工具。首先,对上游而言,IC设计极度复杂,不使用EDA无法实现。

从设计、最优化、分析到仿真,都必须依赖EDA。越是复杂的设计,EDA的必要性就越高,也因此目前存在有众多EDA,EDA本身也都十分复杂。例如编译工具为了调整0到1间的众多变量,必须控制数千个开关。各个开关的调整都必须具备深厚的EDA知识,要求设计人员完全掌握各个功能如何使用负担沉重,也因此必须寻求厂商的应用工程师(AE)协助。此外,要是光靠AE的协助无法解决问题时,必须进一步借助工程师的力量。面对极度严苛的设计环境,必须具备众多相关功能knowhow;然而为了对台湾内部面对相关课题的众多中小企业提供协助,即使是大型EDA提供厂商也不见得拥有所有必要的资源。因此ITRI与大型EDA供应商合作,在内部设置实验室,致力支援台湾中小企业。

也许有点离题,但设计与工具的相关性其实十分重要。由于目前出现众多崭新设计方法, EDA供应商为了将工具升级,必须理解相关设计方法。如果我没记错,2000年前后曾经出现一波电源门控(power gating)※6 风潮。但当时的EDA无法对应电源门控,设计公司开发门控相关技术时必须手动输入。相关事实也恰巧证明了要是设备供应商无法理解设计人员的设计型态,就无法开发EDA工具。

正如前述,设备供应商如果想提升EDA的技术水平,必须针对调试(debug)寻求设计人员协助。据我所知,有几家企业准备着手开发EDA,为了从多元角度出发调试,势必需要寻求众多用户协助,过程应该十分严苛。设计人员的设计方法不一而足,但也正因为如此,必须由设计人员实际使用工具,尝试错误,才能找出问题所在。

对代工厂商而言,EDA也扮演重要角色。由于代工厂商必须对设计人员提供工艺设计包(PDK)※7,EDA有助于将代工厂商相关信息转换为设计人员需要的PDK。为了对设计人员提供最新工艺信息,必须具备代工厂商先进制造技术的相关knowhow,才能考量PDK,设计出高良率的芯片。目前台积电正在推动2纳米、3纳米制程,过程中的微调需要取得众多EDA相关协助。要是能获得供应商合作,可望加速流程微调,降低达成高良率的难度。ITRI与各家供应商合作设置实验室,今后也将通过此实验室,继续扮演台湾半导体发展的幕后推手。

【注释】

磁阻式随机存取记忆体是非易失性记忆体,能高速读写,并且集成程度和耐久性高,耗电量低,耐辐射等优点众多

后段制程的半导体封装加工中,进行树脂封装时部分需要压缩

高性能垂直互联技术,通过单一芯片内的穿透孔,在多张积层晶片间传送信号、电源

指的是WLP的Fan-Out或2.5D实际封装的设备结构中,以Cu与绝缘层形成的配线层。又名重新布线层,串联半导体芯片与外部衔接部分

细管状物体(毛细管)内侧的液体未获来自外部的能量,却能在管中移动的物理现象

集成电路设计用技术,遮蔽未使用的电路区块电流,以降低功耗

特定半导体制程设计中的电路设计用文档资料群